智多晶MCU硬核IP全面升级|CM3和STAR新特性介绍

更统一的架构、更灵活的总线、更简洁的配置——智多晶MCU硬核IP全面升级

随着嵌入式系统复杂度不断提升,FPGA内置MCU硬核已成为主流方案。智多晶针对SA5Z-30和SA5Z-50系列芯片的MCU IP进行了重大升级,不仅在底层架构上实现了突破,更在易用性和扩展性上带来了显著提升。本文将为您详细介绍Cortex-M3(CM3)与STAR Processor的最新特性。

一、架构重组

CM3和STAR的IP做了整合,在接口上统一了命名,可有效提高代码复用以及移植效率。

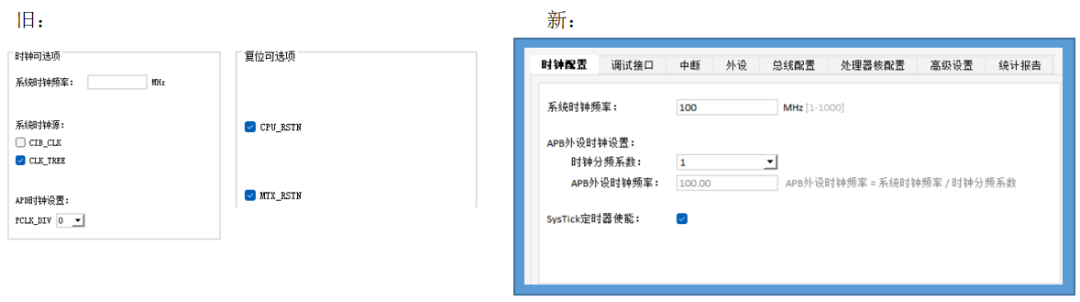

二、配置界面优化

1、单一时钟输入,单一复位输入,省去之前的时钟源选择与复位勾选。

2、GPIO与外设配置革新,除2个必要勾选项外,全部通过表格按键完成配置,支持横向与纵向按键操作,符合不同工程师的操作习惯,同时合并ADC模块,使用MCU的ADC功能时无需再单独例化。

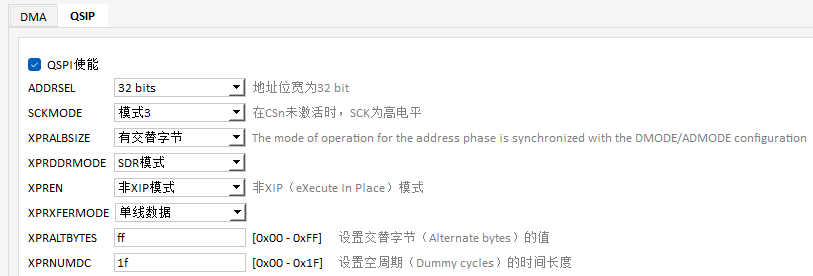

3、优化界面描述,如QSPI的ADDRSEL选项从抽象的"TRUE/FALSE"改为直观的"24bits/32bits"),降低配置出错概率。

三、总线支持

新版IP在总线接口方面作了扩展,现支持AHB、APB、AXI-full、AXI-lite四种主流协议,AHB与APB接口支持扩展至16个,AXI接口支持互联模式,可灵活配置接口数量。支持总线跨时钟域处理能力,解决FPGA逻辑与MCU核心不同时钟域的数据同步难题。

四、丰富的Demo生态

为加速用户上手,智多晶同步推出了21个参考Demo(2025年11月初的HQ版本已支持范例工程输出,并持续更新),涵盖从基础外设到复杂总线扩展的大部分场景。

梦金指南网

梦金指南网